Testing and Co-Design of AI/ML Simulation Processors

Release Time:

2022-08-23

Author:

Source:

Summary

According to reports, as the industry continues to push forward, a large number of new concepts and technologies related to machine learning (ML) and artificial intelligence (AI) are emerging. Among them, analog computing has been reintroduced as a method to improve processing efficiency.

This technology is relatively new for given applications and still has significant room for improvement. Researchers at IISC have published a paper describing a new scalable chip framework for analog AI in the future.

This article will discuss the benefits and challenges of analog computing for artificial intelligence and the new research from IISC addressing these challenges.

Why switch to analog?

Analog computing BSS123 is a technology that predates digital computing, but it was largely forgotten with the rise of digital computing. Now, researchers are refocusing on analog because it has advantages over digital in certain aspects.

With data speeds increasing, processing nodes becoming smaller, and the global internet expanding, a new industry trend is the significant increase in energy consumption corresponding to data movement.

The physical movement of data inside and outside memory has become one of the most important factors in overall chip power consumption. Additionally, for data-intensive applications like ML, we find that the von Neumann architecture is no longer suitable for AI/ML.

In contrast, analog computing allows computation within memory, where data can be processed at the storage location. Because overall data movement is significantly reduced, overall energy consumption is also greatly lowered. Therefore, in AI/ML applications, analog AI can provide AI energy efficiency that is 100 times higher than traditional digital methods.

Challenges of Analog AI: Scaling

Before becoming a competitor to digital computing, analog computing, despite its energy efficiency advantages, still faces some challenges.

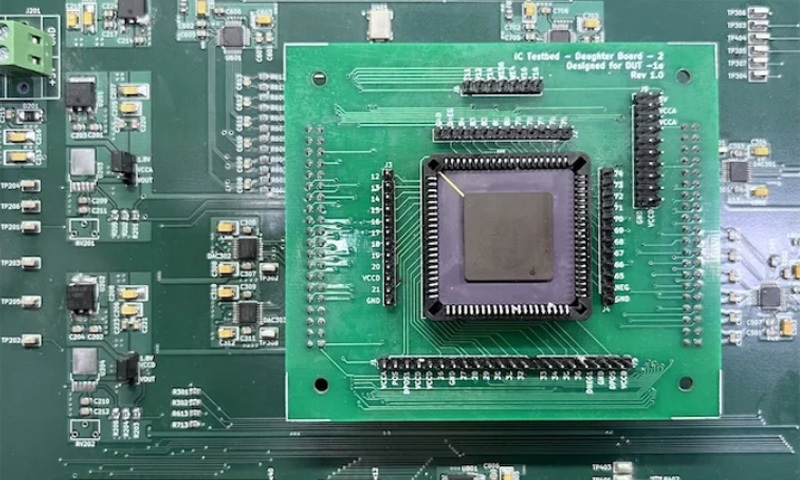

Testing and co-design of AI/ML analog processors is one of the key challenges in analog computing design. Traditional very-large-scale integration (VLSI) design can consist of millions of transistors, but engineers can synthesize designs by compiling high-level code. This capability allows the same design to be easily ported across different process nodes and products.

However, due to transistor bias, temperature variations, and limited dynamic range, analog chips are not easily scalable. Therefore, each generation of product and each process node requires custom design and redesign. This not only makes design more time-consuming and expensive but also reduces scalability.

For analog AI to become mainstream, the challenges of design and scalability must first be addressed.

IISC's AI Scaling Framework

To address this issue, IISC researchers proposed a new scalable analog computing design framework in their recently published paper.

The key to their work revolves around the generalization of message passing (MP), a mathematical tool used to synthesize analog piecewise linear computing circuits, reflecting the principle of value. Based on this, researchers developed a new shape-based analog computing (S-AC) method that allows researchers to simulate ML frameworks commonly used in different architectures.

This framework can make the same trade-offs between computational accuracy and speed/power consumption as digital designs, and it can also span different process nodes and bias management.

Researchers implemented several targets to demonstrate the feasibility of S-AC circuits corresponding to common mathematical functions in ML across different process nodes. The results show that in the 180nm CMOS process and 7nm FinFET, the circuit I/O characteristics remain consistent within a reasonable range during this process.

With the new framework, researchers hope to achieve more scalable and cost-efficient analog AI designs in the near future.

Keywords:

Related Information

发布时间:2020-08-25

发布时间:2020-08-25

发布时间:2020-08-25